Capítulo 5: Estructura del sistema operativo (Parte 2)

Gestión de Entrada/Salida

En un sistema informático moderno podemos encontrar muchos dispositivos de entrada/salida diferentes. Sin embargo, uno de los objetivos del diseño de un sistema operativo es que el usuario, o el programador, los perciban de una forma parecida, sin importar los detalles técnicos que los distinguen ni la diferencia en cuanto a la complejidad del dispositivo.

En el capítulo 1 establecíamos una primera clasificación de los dispositivos en función de si eran de entrada, de salida o de entrada/salida. Sin embargo, también podríamos clasificarlos según la parte del sistema informático con la que se comunican:

-

Dispositivos legibles por los usuarios (como teclados, monitores, impresoras, ratones, etc).

-

Dispositivos legibles por el ordenador (como discos, dispositivos USB, unidades ópticas, sensores, etc).

-

Dispositivos de comunicaciones (como modems, routers, adaptadores 3G/4G, etc.)

Otra forma de clasificarlos estaría en función de la velocidad a la que transmiten sus datos, ya que hay mucha diferencia, por ejemplo, entre dispositivos como un teclado, un disco óptico, un disco duro o un monitor. En cualquier caso, todos los dispositivos de entrada/salida son mucho más lentos que la memoria principal.

Incluso podríamos centrarnos en el modo de transferencia, ya que algunos dispositivos reciben los datos por bloques (como el disco duro) y otros byte a byte (como los dispositivos USB).

Por último, algunos dispositivos pueden utilizarse para diferentes fines (un disco duro puede almacenar datos, una imagen, una copia de seguridad, páginas de memoria principal, etc).

Todo ello, nos ofrece una idea de lo complejo que es el trabajo de la entrada/salida en un sistema operativo actual.

Técnicas para llevar a cabo las operaciones de entrada/salida

Un ordenador puede utilizar diferentes técnicas para interactuar con los controladores de entrada/salida. Como ya hicimos en el apartado anterior, vamos a nombrar las más representativas de menor a mayor sofisticación:

-

Entrada/salida programada: El procesador ejecuta una instrucción de un proceso que solicita una operación de entrada/salida. Se realiza el requerimiento al módulo de entrada/salida correspondiente, y queda en espera de recibir la respuesta.

-

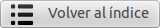

Entrada/salida controlada por interrupciones: El procesador ejecuta una instrucción de un proceso que solicita una operación de entrada/salida. Entonces, el proceso espera en estado Bloqueado y el procesador continúa con la ejecución de otras instrucciones. Cuando se completa la operación, el módulo de entrada/salida genera una interrupción para el procesador y éste ejecuta el módulo del sistema operativo que pone al proceso en estado Listo.

En ocasiones, un mismo proceso puede estar dividido en diferentes hilos de ejecución, que se planifican de forma independiente. En estos casos, puede que un hilo de un proceso realice una solicitud de entrada/salida y que otro hilo siga ejecutándose sin que el proceso quede bloqueado.

-

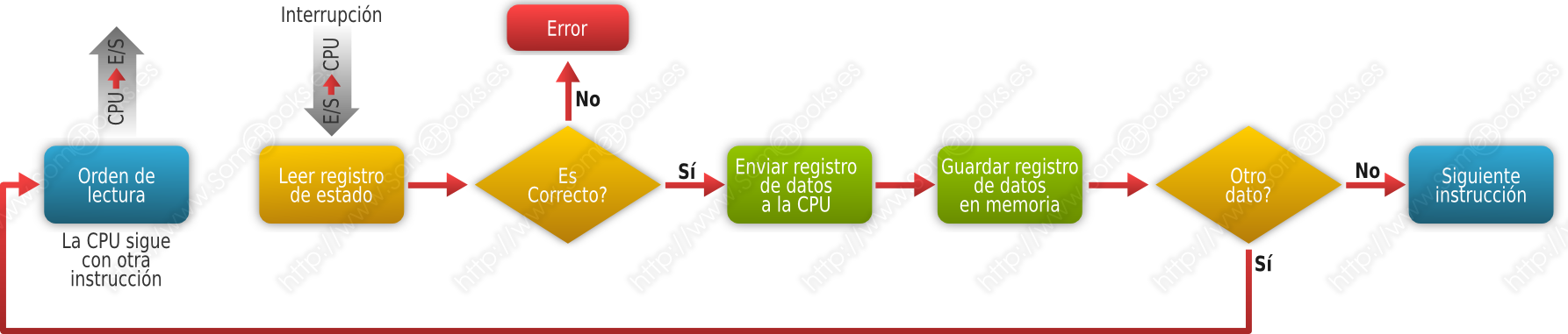

Acceso directo a memoria (o DMA, del inglés Direct Memory Access): El equipo dispone de un módulo DMA autorizado para acceder directamente a la memoria RAM. De esta forma, en lugar de encargarse el procesador de controlar cada operación individual de entrada o salida, se confía en el módulo DMA para que ejecute varias operaciones consecutivas poniendo (u obteniendo) la información directamente en la memoria RAM. El módulo DMA interrumpe al procesador sólo cuando han acabado todas las operaciones que tenía encargadas.

Un posible inconveniente del acceso directo a memoria es que puede generar un uso intensivo del bus del sistema. Como consecuencia, éste puede estar ocupado cuando el procesador trate de obtener datos e instrucciones de la memoria, lo que afectará al rendimiento general del sistema.

Existen dos enfoques diferentes para este problema:

-

Transferencias por robo de ciclo: Se utiliza cuando el procesador no tiene memoria caché interna o ésta es de escaso tamaño. El procesador cede el uso del bus al DMA, que lo libera después de transferir una palabra. Después tendrá que volver a esperar una nueva concesión del procesador. Este proceso se repite hasta que se complete la transferencia.

Si el procesador no dispone de ninguna memoria caché, cada vez que el DMA toma el control, el ciclo de instrucción quedará suspendido y el procesador quedará a la espera durante un ciclo de bus, pero no se produce ninguna interrupción, por lo que no se produce un cambio de contexto.

-

Transferencias por ráfagas: Se utiliza cuando el procesador dispone de memoria caché interna suficiente. Mientras el procesador accede a los datos guardados en ella, el bus del sistema permanece disponible para el DMA, que no lo libera hasta que finaliza la transferencia.

Este método ofrece un alto rendimiento del acceso directo a memoria.

-

Procesadores de entrada/salida (o IOP, del inglés Input/Output Processor): El equipo dispone de un procesador complementario con la capacidad de ejecutar las operaciones de entrada/salida, obteniéndolas directamente de la memoria principal. También puede utilizar técnicas de DMA para leer o escribir los datos en la memoria. De esta forma, el procesador principal queda liberado de este tipo de operaciones.

Concepto de almacenamiento intermedio

Ya comentamos en el primer capítulo que los dispositivos de almacenamiento secundario son mucho más lentos que la memoria principal. En aquél momento hablábamos de que la memoria caché puede aprovechar el principio de cercanía de referencias para agilizar el acceso a datos entre el procesador y la memoria principal, y entre ésta y el almacenamiento secundario.

Sin embargo, cuando es necesario leer un gran volumen de datos del almacenamiento secundario, el proceso irá emitiendo solicitudes de bloques de manera consecutiva, que irá procesando de uno en uno. Como el almacenamiento secundario es mucho más lento, entre una lectura y otra el proceso, probablemente, permanecerá en estado Bloqueado. Una vez completada la lectura, tendrá que esperar en la cola de procesos en estado Listo hasta que el Planificador lo elija para su ejecución.

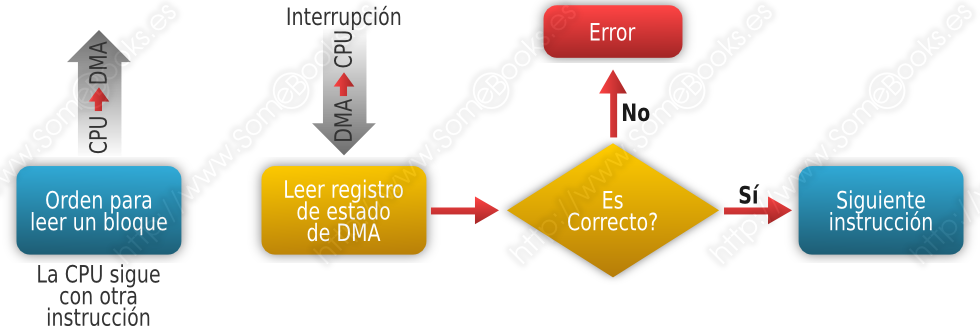

Para evitar esta situación, se utiliza una técnica denominada buffering, que consiste en que el sistema operativo realice las lecturas antes de que se produzca la solicitud, almacenándolas en un área de la memoria principal que recibe el nombre de Buffer.

En este caso, se trataría de un buffer de entrada, porque hemos puesto como ejemplo un proceso en el que se leen datos, pero se pueden aplicar las mismas consideraciones para procesos que escriban datos. En estos casos, las escrituras se realizarán un tiempo después de que se haya producido la solicitud, y se utiliza un buffer de salida.

Con dispositivos orientados a bloques, una mejora consiste en utilizar una memoria intermedia doble o memoria intermedia de intercambio. La idea radica en utilizar dos almacenamientos intermedios. Así, mientras el proceso lee o escribe en uno de ellos, el sistema operativo rellena o desocupa el otro.

Para dispositivos orientados a caracteres, o aquellos en los que la transferencia se realiza en ráfagas de gran velocidad, pueden utilizarse más de dos memorias intermedias dispuestas de forma circular, siguiendo un modelo denominado productor/consumidor.

Algo parecido puede hacerse cuando disponemos de dispositivos muy lentos que, sin embargo, pueden recibir grandes volúmenes de datos. En estos casos, puede utilizarse una memoria intermedia situada en un almacenamiento externo (típicamente, un disco) e ir enviando los datos poco a poco al dispositivo externo. Esta técnica, aunque es parecida al buffering, recibe el nombre de spooling y la memoria intermedia recibe el nombre de spool (del inglés, Simultaneous Peripheral Operations On-Line). Es una técnica que se utiliza habitualmente con las impresoras.